Quaturs라는 회로설계 프로그램으로 지하철 승차권 자판기를 만드는 것이였다.

3인 1조로 팀을 구성했는데, 프로젝트상에서 조합회로 전체와 메모리를 설계했다.

설계 한다음에 SoC 보드에 올려서 작동하는 것을 확인하는 것이 목표다.

서브블록을 하나씩 검증해 가면서 합쳐 나갈 때 즐거움을 느꼈다.

마감 전날 밤을 새며 아침에 완성했다. 오후에 검사 맡았는데 집에도 못가고 학과 독서실에서 엎드려 자면서 기다렸다.

기말고사 끝나고 방학인데 이거 한다고 며칠 집에 못가고 고생했다.

문제는 이 프로그램으로 회로를 마우스로 하나씩 그려가면서 했는데

3학년 되서 보니 Verilog HDL이라는 프로그램이 있어서 C언어 처럼 고크 몇줄로 그런 회로를 구현 한다는 사실에 충격 받았다.

물론 실무에서 이렇게 손으로 그릴일은 없겠지만 적어도 이렇게 그려봄으로써 회로와 더 친해 질 수 있었던 것 같다.

당시 사진도 찍고 캡쳐해서 컬러 문서로 만들어 놨는데, 그것을 저장해둔 USB가 날라가서 지금 Hard copy된 흑백 출력본을 다시 스캔해서 사진을 올린다.

ASM 차트이다. 자판기에 동전을 넣는 순간 부터 어떻게 작동하는지 순서를 볼 수 있다.

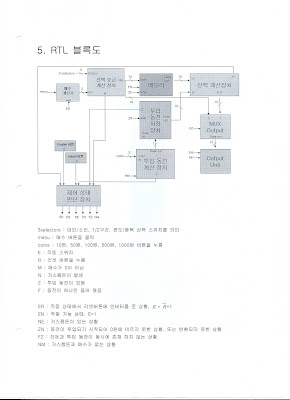

RTL 블럭도이다. 실제 회로를 그리기 전에 어떻게 control이 되는지 개념적으로 그린 것이다.

실제 설계한 회로이다.

흑백으로 출력된 것을 다시 스캔하니 이렇다. LED 색상은 빨간색이다.

2 comments:

balenciaga shoes

longchamp

jordan shoes

kyrie shoes

kobe shoes

vapormax

coach outlet online

curry 4

timberland

michael kors purses

see page replica gucci bags have a peek at this web-site louis vuitton replica weblink replica bags online

Post a Comment